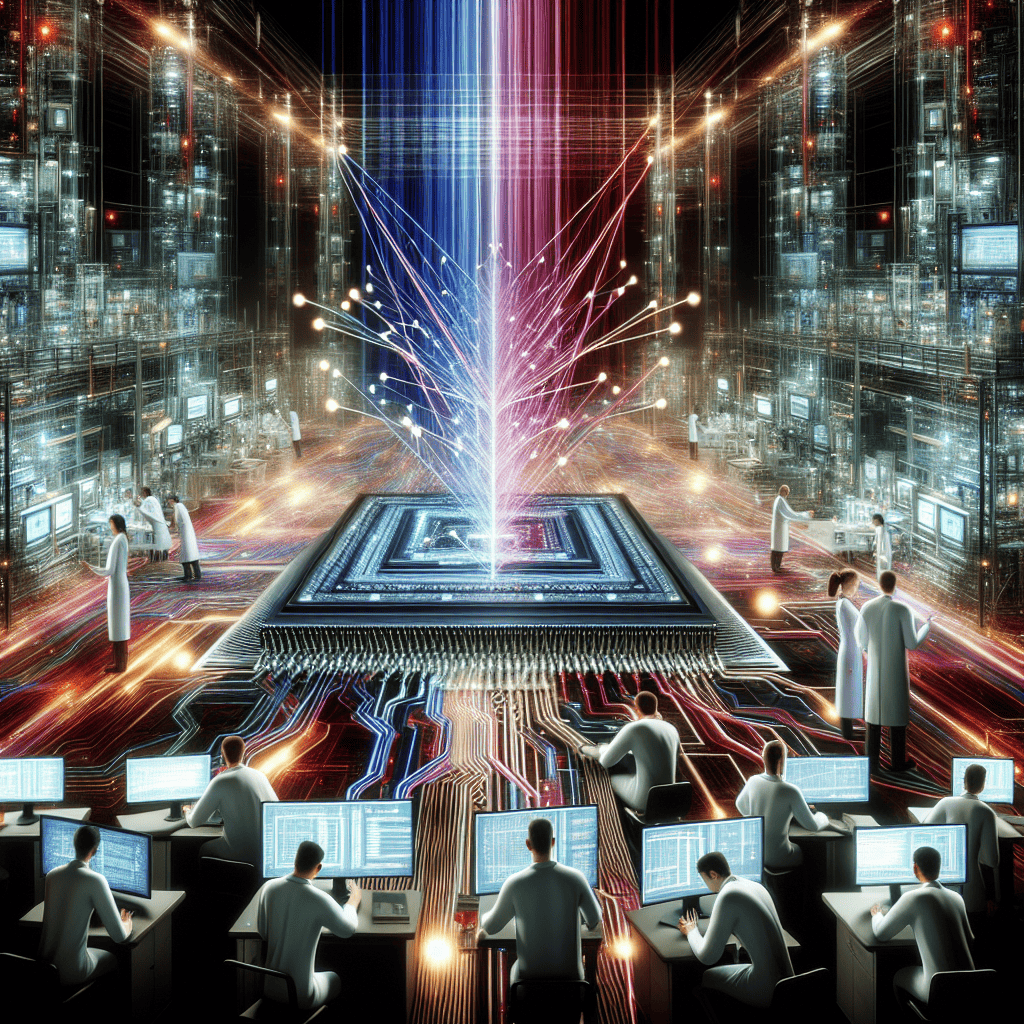

MIT engineers have made significant advancements in semiconductor technology by developing a vertical 3D chip architecture. This innovative approach allows for the stacking of multiple layers of circuits, enhancing performance and efficiency while reducing the physical footprint of electronic devices. By utilizing vertical integration, the new chip design aims to overcome the limitations of traditional planar chips, enabling faster data processing and improved energy efficiency. This breakthrough has the potential to revolutionize various applications, from consumer electronics to advanced computing systems, paving the way for more powerful and compact devices in the future.

MIT Engineers Revolutionize Computing with Vertical 3D Chip Technology

In a groundbreaking advancement in the field of computing, engineers at the Massachusetts Institute of Technology (MIT) have developed a novel vertical 3D chip technology that promises to significantly enhance the performance and efficiency of electronic devices. This innovative approach to chip design addresses the growing demand for faster processing speeds and increased data storage capabilities, which are essential in an era characterized by rapid technological evolution and the proliferation of data-intensive applications.

Traditionally, semiconductor chips have been designed in a two-dimensional layout, which, while effective for many years, has begun to reach its physical and performance limits. As transistors shrink to nanoscale dimensions, the challenges associated with heat dissipation, power consumption, and signal integrity have become increasingly pronounced. In response to these challenges, the MIT team has pioneered a vertical stacking method that allows multiple layers of chips to be integrated in a three-dimensional configuration. This vertical arrangement not only optimizes space but also enhances the interconnectivity between layers, thereby facilitating faster data transfer and improved overall performance.

One of the key advantages of this vertical 3D chip technology is its ability to significantly reduce the distance that electrical signals must travel. By stacking chips vertically, the MIT engineers have minimized the length of interconnections, which in turn reduces latency and power consumption. This is particularly important in applications such as artificial intelligence and machine learning, where rapid data processing is crucial. As a result, devices utilizing this technology can perform complex computations more efficiently, leading to faster response times and improved user experiences.

Moreover, the vertical 3D chip design allows for greater flexibility in chip architecture. Engineers can customize the arrangement of different functional units within the stack, enabling the creation of application-specific integrated circuits (ASICs) that are tailored to meet the unique demands of various applications. This adaptability not only enhances performance but also opens the door to innovative designs that were previously unattainable with traditional 2D chips.

In addition to performance improvements, the vertical 3D chip technology also holds promise for sustainability in computing. As the demand for energy-efficient solutions grows, this new approach can contribute to reducing the carbon footprint of electronic devices. By decreasing power consumption and improving thermal management, the technology aligns with global efforts to create more environmentally friendly computing solutions. This is particularly relevant in light of increasing scrutiny on the energy consumption of data centers and the broader tech industry.

Furthermore, the implications of this technology extend beyond consumer electronics. Industries such as telecommunications, automotive, and healthcare stand to benefit from the enhanced capabilities offered by vertical 3D chips. For instance, in the realm of autonomous vehicles, the need for rapid data processing from numerous sensors can be met more effectively with this advanced chip architecture. Similarly, in healthcare, the ability to process large volumes of data quickly can lead to improved diagnostic tools and patient care solutions.

In conclusion, the development of vertical 3D chip technology by MIT engineers represents a significant leap forward in the quest for more powerful and efficient computing solutions. By addressing the limitations of traditional chip designs and offering a versatile, sustainable alternative, this innovation is poised to reshape the landscape of electronics and computing. As industries continue to evolve and demand for advanced technologies grows, the impact of this revolutionary approach will likely be felt across various sectors, paving the way for a new era of computing excellence.

The Future of Electronics: Vertical 3D Chip Innovations by MIT

In recent years, the demand for more efficient and powerful electronic devices has surged, prompting researchers and engineers to explore innovative solutions that can meet these growing needs. Among the most promising advancements in this field is the development of vertical 3D chip technology by engineers at the Massachusetts Institute of Technology (MIT). This groundbreaking approach to chip design not only addresses the limitations of traditional planar architectures but also paves the way for a new era of electronics characterized by enhanced performance and reduced energy consumption.

The traditional two-dimensional chip design has served the electronics industry well for decades; however, as devices become increasingly complex and the demand for higher processing power escalates, the limitations of this architecture have become apparent. In response to these challenges, MIT engineers have turned their attention to vertical 3D chip technology, which allows for the stacking of multiple layers of circuitry. This innovative design significantly increases the density of components within a given footprint, thereby enabling more powerful processing capabilities without the need for larger devices.

One of the key advantages of vertical 3D chip technology is its ability to minimize the distance that electrical signals must travel between components. In conventional chips, signals often have to traverse long pathways, which can lead to delays and increased energy consumption. By stacking layers vertically, MIT’s design reduces these distances, resulting in faster signal transmission and improved overall efficiency. This reduction in signal travel time not only enhances performance but also contributes to lower power requirements, making devices more sustainable and environmentally friendly.

Moreover, the vertical stacking of components allows for greater integration of different functionalities within a single chip. For instance, MIT’s engineers have demonstrated the potential to combine processing units, memory, and even specialized sensors within a compact vertical structure. This level of integration can lead to the development of multifunctional devices that are capable of performing a wide range of tasks, thereby streamlining operations and reducing the need for multiple separate components. As a result, manufacturers can produce smaller, lighter devices that do not compromise on performance.

In addition to these technical advantages, vertical 3D chip technology also holds promise for the future of artificial intelligence (AI) and machine learning applications. As these fields continue to evolve, the need for chips that can handle vast amounts of data at high speeds becomes increasingly critical. The vertical architecture developed by MIT engineers is particularly well-suited for such applications, as it can facilitate rapid data processing and analysis, enabling more sophisticated AI algorithms to run efficiently.

Furthermore, the implications of this technology extend beyond consumer electronics. Industries such as healthcare, automotive, and telecommunications stand to benefit significantly from the advancements in vertical 3D chip design. For example, in healthcare, more efficient chips could lead to the development of advanced medical devices capable of real-time monitoring and analysis, ultimately improving patient outcomes. In the automotive sector, enhanced processing capabilities could support the development of more sophisticated autonomous driving systems.

In conclusion, the vertical 3D chip technology developed by MIT engineers represents a significant leap forward in the field of electronics. By addressing the limitations of traditional chip designs and offering a more efficient, integrated, and powerful alternative, this innovation is poised to transform not only consumer electronics but also a wide range of industries. As research and development in this area continue to progress, the future of electronics looks increasingly promising, with the potential for devices that are not only more capable but also more sustainable.

Enhancing Performance: How MIT’s Vertical 3D Chips Outperform Traditional Designs

In the realm of semiconductor technology, the quest for enhanced performance has led to groundbreaking innovations, one of which is the development of vertical 3D chip technology by engineers at the Massachusetts Institute of Technology (MIT). This novel approach to chip design represents a significant departure from traditional planar architectures, which have dominated the industry for decades. By stacking multiple layers of circuitry vertically, MIT’s engineers have created a more compact and efficient solution that promises to revolutionize the way electronic devices operate.

The primary advantage of vertical 3D chips lies in their ability to significantly reduce the distance that electrical signals must travel. In conventional chip designs, the horizontal layout often results in longer interconnects, which can introduce latency and consume more power. In contrast, vertical stacking minimizes these distances, allowing for faster signal transmission and improved overall performance. This reduction in travel distance not only enhances speed but also contributes to energy efficiency, a critical factor in an era where power consumption is a growing concern for both consumers and manufacturers.

Moreover, the vertical architecture facilitates a higher density of components within a given footprint. As the demand for more powerful and compact devices continues to rise, the ability to integrate more transistors and other components into a smaller space becomes increasingly valuable. MIT’s vertical 3D chips can accommodate a greater number of functional elements without the need for a proportional increase in chip size. This capability not only allows for more complex processing tasks but also enables the development of smaller, lighter devices that can perform at higher levels.

In addition to these performance enhancements, the vertical 3D chip technology also offers improved thermal management. Traditional chip designs often struggle with heat dissipation, as the horizontal layout can lead to hotspots that affect performance and reliability. By stacking layers vertically, MIT’s engineers have created a design that promotes better airflow and heat distribution. This innovation is particularly important in high-performance computing environments, where excessive heat can lead to throttling and reduced efficiency. The ability to manage heat more effectively ensures that devices can maintain optimal performance levels over extended periods.

Furthermore, the vertical 3D chip technology opens up new possibilities for integrating diverse functionalities within a single chip. For instance, it allows for the combination of digital, analog, and memory components in a unified architecture. This integration not only streamlines the manufacturing process but also enhances the performance of applications that require tight coupling between different types of circuitry. As a result, devices can achieve higher levels of functionality while maintaining a smaller form factor.

As the semiconductor industry continues to evolve, the implications of MIT’s vertical 3D chip technology extend beyond mere performance improvements. The potential for reduced manufacturing costs, increased reliability, and enhanced capabilities positions this innovation as a game-changer in the field. As researchers and engineers explore the full range of applications for vertical 3D chips, it is clear that this technology will play a pivotal role in shaping the future of electronics. In conclusion, the advancements made by MIT engineers not only highlight the importance of innovative design in enhancing performance but also underscore the ongoing need for the industry to adapt to the ever-increasing demands of modern technology.

The Impact of Vertical 3D Chip Technology on Data Centers

The advent of vertical 3D chip technology, developed by engineers at the Massachusetts Institute of Technology (MIT), is poised to revolutionize the landscape of data centers. As the demand for data processing and storage continues to escalate, traditional chip designs face significant limitations in terms of space, power consumption, and heat dissipation. Vertical 3D chip technology addresses these challenges by stacking multiple layers of chips vertically, thereby optimizing the use of physical space and enhancing performance.

One of the most significant impacts of this innovative technology is its potential to dramatically increase the density of data centers. By utilizing vertical stacking, data centers can house more processing power within a smaller footprint. This is particularly crucial as organizations strive to maximize their operational efficiency while minimizing real estate costs. The ability to fit more computational resources into a compact area not only reduces the physical space required but also lowers the associated costs of cooling and power supply, which are critical factors in data center management.

Moreover, vertical 3D chip technology enhances data transfer speeds between layers of chips. Traditional horizontal chip designs often suffer from latency issues due to the distance signals must travel. In contrast, the vertical arrangement allows for shorter interconnections, significantly reducing the time it takes for data to move between processing units. This improvement in speed is essential for applications that require real-time data processing, such as artificial intelligence and machine learning, where rapid decision-making is paramount.

In addition to improving speed and density, vertical 3D chip technology also offers substantial energy efficiency benefits. As data centers are notorious for their high energy consumption, the ability to reduce power usage while maintaining performance is a game changer. The stacked architecture minimizes the energy lost in data transmission and reduces the overall power required for cooling systems. Consequently, organizations can achieve a more sustainable operation, aligning with global efforts to reduce carbon footprints and promote environmentally friendly practices.

Furthermore, the integration of vertical 3D chips can lead to enhanced reliability and performance. By consolidating multiple functions into a single chip stack, the technology reduces the number of components that can fail, thereby increasing the overall reliability of the system. This is particularly important for mission-critical applications where downtime can result in significant financial losses. The improved thermal management associated with vertical designs also contributes to longer chip lifespans, further enhancing the reliability of data center operations.

As data centers evolve to accommodate the increasing demands of modern computing, the implementation of vertical 3D chip technology represents a significant leap forward. The ability to stack chips vertically not only addresses the pressing issues of space and energy consumption but also enhances performance and reliability. As organizations continue to seek innovative solutions to manage their data needs, the adoption of this technology is likely to become a standard practice in the industry.

In conclusion, the impact of vertical 3D chip technology on data centers is profound and multifaceted. By enabling higher density, faster data transfer, improved energy efficiency, and enhanced reliability, this technology is set to redefine how data centers operate. As MIT engineers continue to refine and develop this technology, its widespread adoption could lead to a new era of data processing capabilities, ultimately transforming the way businesses manage and utilize their data resources.

MIT’s Breakthrough in Vertical 3D Chip Technology: Implications for AI

In a significant advancement for the field of computing, engineers at the Massachusetts Institute of Technology (MIT) have developed a groundbreaking vertical 3D chip technology that promises to revolutionize the way artificial intelligence (AI) systems are designed and implemented. This innovative approach to chip architecture not only enhances computational efficiency but also addresses the growing demand for more powerful processing capabilities in AI applications. As the complexity of AI algorithms continues to increase, traditional chip designs, which primarily rely on horizontal layouts, face limitations in terms of speed and energy consumption. The introduction of vertical 3D chip technology offers a compelling solution to these challenges.

The essence of this new technology lies in its ability to stack multiple layers of circuitry vertically, thereby significantly increasing the density of transistors within a given footprint. This vertical stacking allows for shorter interconnections between components, which in turn reduces latency and enhances data transfer speeds. As a result, AI systems can process vast amounts of information more rapidly, enabling real-time decision-making and more sophisticated machine learning models. Furthermore, the compact nature of vertical 3D chips means that they can be integrated into smaller devices, paving the way for advancements in mobile AI applications and edge computing.

Moreover, the implications of this technology extend beyond mere performance improvements. The energy efficiency of vertical 3D chips is another critical factor that cannot be overlooked. As AI systems become increasingly prevalent in various sectors, from healthcare to autonomous vehicles, the demand for energy-efficient computing solutions grows. The vertical architecture minimizes power consumption by reducing the distance that electrical signals must travel, thereby lowering the overall energy required for processing tasks. This efficiency is particularly vital in an era where sustainability and environmental considerations are paramount, making vertical 3D chip technology not only a technical innovation but also a step towards greener computing.

In addition to enhancing performance and energy efficiency, MIT’s vertical 3D chip technology opens new avenues for research and development in AI. The increased transistor density allows for more complex neural networks to be implemented directly on the chip, facilitating the exploration of advanced AI models that were previously impractical due to hardware limitations. This capability could lead to breakthroughs in various AI applications, including natural language processing, computer vision, and robotics. As researchers experiment with these new architectures, the potential for discovering novel algorithms and techniques that leverage the unique properties of vertical 3D chips becomes increasingly promising.

Furthermore, the adoption of this technology could have far-reaching implications for the semiconductor industry as a whole. As companies strive to keep pace with the rapid advancements in AI, the demand for innovative chip designs will likely drive competition and collaboration among tech firms. This shift may lead to a re-evaluation of existing manufacturing processes and supply chains, as the industry adapts to accommodate the unique requirements of vertical 3D chip production. Consequently, the ripple effects of MIT’s breakthrough could reshape not only the landscape of AI but also the broader technological ecosystem.

In conclusion, MIT’s development of vertical 3D chip technology represents a pivotal moment in the evolution of computing, particularly in the context of artificial intelligence. By enhancing performance, improving energy efficiency, and enabling new research opportunities, this innovation stands to transform the capabilities of AI systems. As the technology matures and gains traction within the industry, it is poised to play a crucial role in shaping the future of intelligent systems and their applications across various domains.

Exploring the Manufacturing Process of MIT’s Vertical 3D Chips

The manufacturing process of MIT’s vertical 3D chips represents a significant advancement in semiconductor technology, promising to revolutionize the way electronic devices are designed and produced. This innovative approach addresses the limitations of traditional planar chip designs, which have struggled to keep pace with the increasing demand for higher performance and lower power consumption. By stacking multiple layers of circuitry vertically, MIT engineers have created a more compact and efficient architecture that enhances the capabilities of integrated circuits.

To begin with, the manufacturing process involves several key steps that ensure the successful creation of these vertical 3D chips. Initially, engineers utilize advanced lithography techniques to define the intricate patterns of the chip’s circuitry on a substrate. This step is crucial, as it lays the foundation for the subsequent layers that will be added. The precision of this process is paramount, as even the slightest misalignment can lead to significant performance issues in the final product.

Once the initial layer is completed, the next phase involves the deposition of additional materials that will form the subsequent layers of the chip. This is achieved through techniques such as chemical vapor deposition (CVD) and atomic layer deposition (ALD), which allow for the controlled application of thin films. These methods are particularly advantageous in the context of vertical 3D chips, as they enable the creation of highly uniform layers that are essential for maintaining the integrity of the chip’s performance.

Following the deposition of materials, the engineers employ etching techniques to carve out the necessary features within each layer. This step is critical for defining the electrical pathways that will connect the various components of the chip. The etching process must be executed with extreme precision to ensure that the layers align perfectly, thereby facilitating efficient communication between them. As the layers are built up, the complexity of the chip increases, allowing for a greater number of transistors to be integrated into a smaller footprint.

Moreover, the vertical stacking of layers introduces unique challenges that must be addressed during the manufacturing process. For instance, thermal management becomes a crucial consideration, as the increased density of components can lead to heat buildup that may affect performance and reliability. To mitigate this issue, engineers are exploring innovative cooling solutions that can effectively dissipate heat without compromising the chip’s compact design.

In addition to thermal management, the interconnectivity between layers poses another challenge. Traditional methods of connecting layers can be inefficient and may introduce latency in signal transmission. To overcome this, MIT engineers are developing novel interconnect strategies that utilize advanced materials and designs to enhance the speed and efficiency of data transfer between layers. This focus on improving interconnectivity is essential for ensuring that the vertical 3D chips can meet the demands of modern applications, which require rapid processing and high bandwidth.

As the manufacturing process continues to evolve, MIT’s vertical 3D chip technology holds the potential to transform various industries, from consumer electronics to artificial intelligence. The ability to produce more powerful and efficient chips in a smaller form factor could lead to breakthroughs in device performance, enabling new applications and enhancing existing technologies. Ultimately, the advancements made in the manufacturing process of these chips not only reflect the ingenuity of MIT engineers but also pave the way for a future where electronic devices are more capable and versatile than ever before.

Q&A

1. **What is the main innovation of the MIT engineers’ vertical 3D chip technology?**

The main innovation is the ability to stack multiple layers of chips vertically, allowing for increased density and improved performance compared to traditional flat chip designs.

2. **How does vertical stacking benefit chip performance?**

Vertical stacking reduces the distance data must travel between layers, which can lead to faster processing speeds and lower power consumption.

3. **What are potential applications of this vertical 3D chip technology?**

Potential applications include advanced computing systems, artificial intelligence, and high-performance data centers, where space and efficiency are critical.

4. **What challenges does vertical 3D chip technology address?**

It addresses challenges related to heat dissipation, signal integrity, and the limitations of traditional 2D chip designs in scaling performance.

5. **How does this technology impact the future of semiconductor manufacturing?**

It could revolutionize semiconductor manufacturing by enabling more compact designs, reducing material costs, and improving overall chip functionality.

6. **What are the implications for energy efficiency with this new technology?**

The vertical 3D chip technology has the potential to significantly enhance energy efficiency by minimizing power loss and optimizing thermal management in high-performance applications.MIT engineers have developed a groundbreaking vertical 3D chip technology that significantly enhances the performance and efficiency of integrated circuits. This innovation allows for a denser arrangement of components, reducing the distance data must travel and minimizing energy consumption. The vertical stacking of chips not only improves speed but also addresses the limitations of traditional planar designs, paving the way for more powerful and compact electronic devices. This advancement could lead to substantial improvements in various applications, including artificial intelligence, data processing, and consumer electronics, marking a significant step forward in semiconductor technology.